algebraboole

sábado, 5 de mayo de 2012

lunes, 30 de enero de 2012

COMPUERTAS LOGICAS

Compuertas logicas

Las compuertas lógicas realizan funciones con solo 2 condiciones "0" y "1"."0" = FALSE

"1" = TRUE

La mayoría de los cicuitos integrados utilizados en los proyectos de esta página son negativos o NMOS

entonces:

"0" es negativo o 0 voltios y

"1" es igual al voltaje positivo.

En la mayoría de los proyectos y aplicaciones se utilizan 2 tipos de tecnología en compuertas lógicas,

la tecnología TTL y la tecnología CMOS

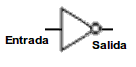

Compuerta NOT

La compuerta lógica "NOT", es el complemento de la compuerta "YES" ya que la condición lógica de la entrada será la inversa en la salida.Por ello es llamado inversor.

Símbolo de la compuerta "NOT":

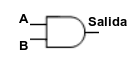

Compuerta AND

La compuerta lógina AND puede ser llamada tambien compuerta "Y" ( i )La salida será "1" si las entradas A "Y" B están en "1"

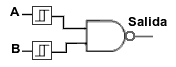

Símbolo de la compuerta "AND":

Tabla de verdad de las compuertas "AND":

| Entrada A | Entrada B | Salida |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

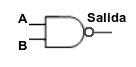

Compuerta NAND

La compuerta lógica "NAND", funciona igual que la compuerta AND pero el resultado en la salida es opuesto.La salida será "0" si las entradas A "Y" B están en "1"

Símbolo de la compuerta "NAND":

Tabla de verdad de las compuertas "NAND":

| Entrada A | Entrada B | Salida |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

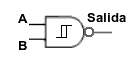

Schmitt trigger

Como en la mayoría de las compuertas lógicas, en tambien existe la versión "Schmitt trigger"Pero en las AND son poco comunes.

Símbolo de compuerta NAND "Schmitt trigger"

La función de Schmitt trigger se ejecuta en las entradas de cada compuerta, el circuito equivalente sería:

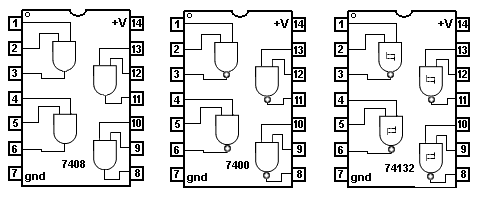

Circuitos integrados con compuertas AND y NAND

Los más comunes los represento en estos diagramas o dibujos:

Diagrama de las conexiones de las compuertas CMOS

| Compuertas AND | Compuertas NAND | Compuertas NAND Schmitt trigger |

Tecno_ logía |

|---|---|---|---|

| 4081 | 4011 | 4093 | CMOS |

| 7408 | 7400 | 74132 | TTL |

Diagrama de las conexiones de las compuertas TTL:

Las compuertas lógicas NAND son muy utilizadas y podemos diseñar una gran variedad de proyectos digitales con ellas.

Compuertas lógicas OR y NOR

Compuerta OR

La compuerta lógica OR puede llamarse también compuerta lógica "o"La salida será "1" si la entrada A "o" la entrada B están en "1"

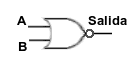

Símbolo de la compuerta "OR":

Tabla de verdad de las compuertas "OR" :

| Entrada A | Entrada B | Salida |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Compuerta NOR

La compuerta lógica "NOR",Su función es igual que OR pero su salida invertida.

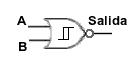

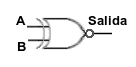

Símbolo de la compuerta "NOR":

Tabla de verdad de las compuertas "NOR" :

| Entrada A | Entrada B | Salida |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Schmitt trigger

Aunque tambien existe la versión de compuertas lógicas OR o NOR "Schmitt trigger" no es común encontrar circuitos integrados con ellas individualmente.Símbolo de compuerta NOR "Schmitt trigger"

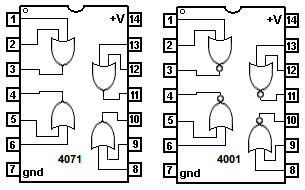

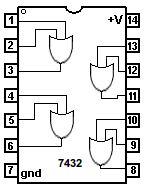

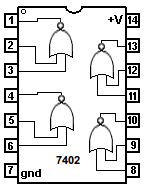

Circuitos integrados con compuertas OR y NOR

Los más comunes los represento en estos diagramas o dibujos:

Notese que las conecciones de los pines en los circuitos integrados CMOS y TTL son diferentes.

Diagrama de las conexiones de las compuertas CMOS:

| Compuertas OR | Compuertas NOR | Tecno_ logía |

|---|---|---|

| 4071 | 4001 | CMOS |

| 7432 | 7402 | TTL |

Diagrama de las conexiones de las compuertas TTL:

Las compuertas lógicas NOR son muy utilizadas y podemos diseñar una gran variedad de proyectos digitales con ellas.

Estas secciones de compuertas lógicas se encuentran en desarrolo y se actualizarán a menudo.

Pronto agregaré algunos ejemplos de proyectos y conexiones prácticas con inversores y buffers.

(28-junio-2010)

Compuertas lógicas XOR y XNOR

Compuerta XOR o compuerta OR Exclusiva.

La compuerta lógica XOR realiza una comparación de las entradassiendo el resultado 0 si las entradas son iguales o 1 cuando son diferentes.

Debemos prestar atención para no confundir el funcionamiento porque esperamos que el resultado sea 1 cuando son iguales.

Símbolo de la compuerta "XOR":

Tabla de verdad de las compuertas "XOR" :

| Entrada A | Entrada B | Salida |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Compuerta XNOR o NOR Exclusiva

La compuerta lógica "XNOR",Es llamada compuerta lógica de EQUIVALENCIA, porque su salida es "1" cuando las entradas se encuentran en el mismo estado.

Su función es igual que XOR pero su salida invertida.

Símbolo de la compuerta "XNOR":

Tabla de verdad de las compuertas "XNOR" :

| Entrada A | Entrada B | Salida |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

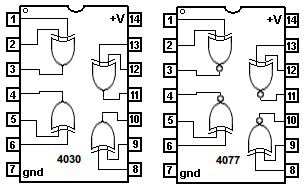

Circuitos integrados con compuertas OR y NOR

Los más comunes los represento en estos diagramas o dibujos:

Notese que las conecciones de los pines en el circuito integrado 7486 son diferentes.

Diagrama de las conexiones de las compuertas CMOS:

| Compuertas XOR | Compuertas XNOR | Tecno_ logía |

|---|---|---|

| 4030 | 4077 | CMOS |

| 7486 | 74HC7266 | TTL |

Diagrama de las conexiones de las compuertas TTL:

En compuertas XNOR es común el circuito integrado 74HC266 que es similar a 74HC7266 pero la salida es a colector abierto y en la mayoría de los casos hay que colocar una resistencia a positivo (pull-up resistor).

La resistencia R1 para pruebas de proto board puede se de 10K, pero para aplicaciones de mayor velocidad hay que utilizar menos resistencia.

Estas secciones de compuertas lógicas se encuentran en desarrolo y se actualizarán a menudo.

Pronto agregaré algunos ejemplos de proyectos y conexiones prácticas con inversores y buffers.

(28-junio-2010)

sábado, 28 de enero de 2012

TABLA DE VERDAD

LOS CUADROS ADYESANTES

En el momento de la lectura, se

rodean los "1" de los cuadros adyacentes mediante un bucle o lazo, que

indica que estos "1" se agrupan para obtener una expresión

simplificada de la función. Los lazos deben cubrir el mayor

número de "1" tomados en potencias de dos. En caso que un "1" no

sea adyacente con ningún otro, se tomará solo.

Veamos las siguientes situaciones:

Veamos las siguientes situaciones:

En la figura (a) f(x, y, z, v) = x' y' v + x z' v' + x' y z v'.

En la figura (b) f(x, y, z, v) = y' v' + y v.

En la figura (c) f(x, y, z, v) = z' v + y' z v'.

En la figura (d) f(x, y, z, v) = y v'.

En ocasiones ocurrirá lo siguiente:

MAPAS DE KARNAUGH

Mapas de Karnaugh. Las formas normales

disyuntivas y conjuntivas son útiles para varios propósitos,

tales como determinar si dos expresiones representan la misma función

booleana. Para otros propósitos son a menudo engorrosas por tener

mas operaciones de las necesarias. Un método para lograr definir

una expresión más simple que otra es el método de

los mapas de karnaugh que simplemente son diagramas de Venn con

las distintas regiones arregladas en cuadros dentro de un rectángulo.

Para funciones de más de cinco variables, este método se vuelve muy complicado y pierde utilidad.

A continuación se verán las diferentes clases de mapas de Karnaugh.

Mapa de una variable,

Mapa de dos variables

Mapa de tres variables

Mapa de cuatro variables

Para funciones de más de cinco variables, este método se vuelve muy complicado y pierde utilidad.

A continuación se verán las diferentes clases de mapas de Karnaugh.

Mapa de una variable,

Mapa de tres variables

Mapa de cuatro variables

Introducción de

términos en mapas de Karnaugh. Cada cuadro en un mapa de

Karnaugh contiene un "1" sí el término representado en ese

cuadro se encuentra en la forma normal disyuntiva de la función. La

siguiente fórmula proporciona el número de "1"s que debe

introducirse en los mapas de Karnaugh.

2N-Q donde N es el número de

variables de la función, Q es el número de variables del

término.

Ejemplo 2.

Dado f(x, y, z, w) = x' y z 'w + x y' z + y z' + x.

El primer término de f da origen a un solo "1" porque 24-4 es igual a 1.

El segundo término de f da origen a dos "1" porque 24-3 es igual a 2.

El tercer términos de f da origen a cuatro "1" porque 24-2 es igual a 4.

El cuarto término de f da origen a ocho "1" porque 24-1 es igual a 8.

Ejemplo 2.

Dado f(x, y, z, w) = x' y z 'w + x y' z + y z' + x.

El primer término de f da origen a un solo "1" porque 24-4 es igual a 1.

El segundo término de f da origen a dos "1" porque 24-3 es igual a 2.

El tercer términos de f da origen a cuatro "1" porque 24-2 es igual a 4.

El cuarto término de f da origen a ocho "1" porque 24-1 es igual a 8.

Ejemplo 4.

Lleve a mapas de Karnaugh la siguiente función.g(x, y, z, w) = x' y z' w +

y z' + x' w.

Solución.

Ejemplo 5.

Lleve a mapas de Karnaugh la siguiente función.

h(x, y, z, v) = x y +

z'.

Solución.

Lleve a mapas de Karnaugh la siguiente función.

Ejemplo 5.

Lleve a mapas de Karnaugh la siguiente función.

Suscribirse a:

Comentarios (Atom)